数字IC除法器结构详解

创作时间:

作者:

@小白创作中心

数字IC除法器结构详解

引用

CSDN

1.

https://blog.csdn.net/qq_43433724/article/details/139069564

在数字电路设计中,除法器是一个重要的算术单元。本文将详细介绍如何通过Verilog实现一个简单的数字IC除法器,包括其工作原理、代码实现以及仿真测试。

在数字电路中,如何可以实现除法器呢?

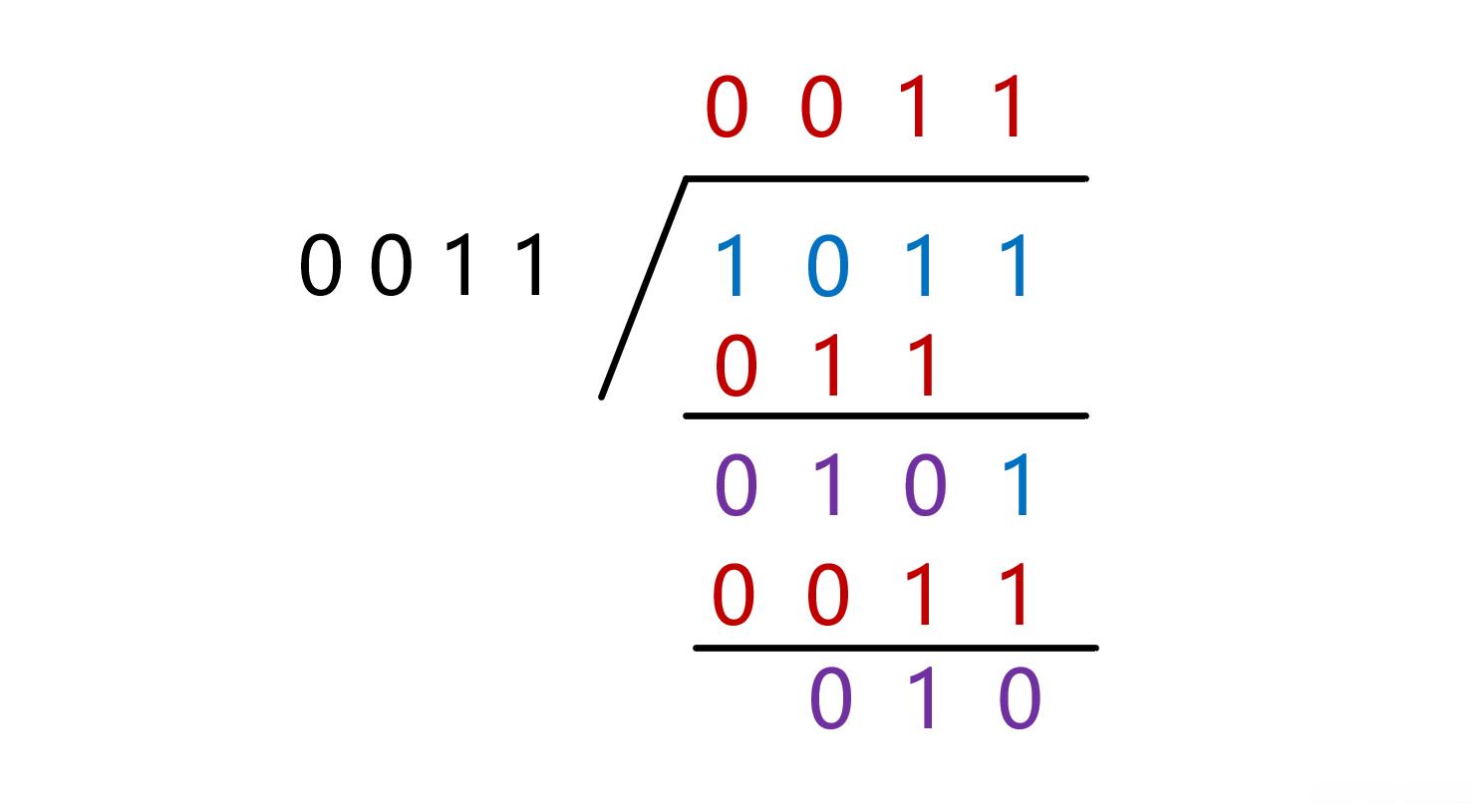

我们先以二进制除法的运算过程为例:

上图中,蓝色表示被除数,红色表示商,紫色表示余数。

如1011(十进制11)除以0011(十进制3)的运算过程,首先从最高位开始,第一位是1,显然不够除以0011,因此本位的商为0,然后扩展下一位变为10依然不够,商继续为0,再扩展一位变为101,此时大于0011,因此将商置1,得到余数010;然后扩展下一位,变为0101,得到商为1,余数为010,因为到了最低位,因此计算完毕,最终结果商为011(十进制3),余数为010(十进制2)。

因此,我们可以通过将上述的算法过程用verilog实现,得到一个除法器。

核心要素如下:

移位

移位表示要从最高位开始和除数进行比较,每比较一次,就需要将下一bit扩展进来

比较器

判断扩展后的数是否大于除数,如果是则商置1

加法器/减法器

用于计算余数以及商

给出如下算法步骤:

①判断最高位temp是否大于除数,是则商加1,余数=temp-除数;否则temp={temp,被除数左移一位后的最高bit};

②循环判断n次。

Verilog如下:

module division(

input clk,

input rst,

input [3:0]a,

input [3:0]b,

input valid,

output reg [3:0]quotient,

output reg [3:0]remainder,

output reg result_valid

);

reg start;

reg start_dl;

reg start_dl2;

reg [1:0]cnt;

reg [3:0]temp;

reg [3:0]quotient_tmp;

always@(posedge clk or posedge rst)

begin

if(rst)

start<=0;

else if(cnt==3'd3)

start<=0;

else if(valid)

start<=1'b1;

else

start<=start;

end

always @(posedge clk or posedge rst)

begin

if(rst)

begin

start_dl <= 0 ;

start_dl2 <= 0 ;

end

else

begin

start_dl <= start ;

start_dl2 <= start_dl ;

end

end

reg [3:0]a_reg;

reg [3:0]b_reg;

always@(posedge clk or posedge rst)

begin

if(rst)

begin

a_reg<=0;

b_reg<=0;

end

else if(start)

a_reg<=a_reg<<1;

else if(valid)

begin

a_reg<=a;

b_reg<=b;

end

else

begin

a_reg<=0;

b_reg<=0;

end

end

always@(posedge clk or posedge rst)

begin

if(rst)

cnt<=0;

else if(start)

cnt<=cnt+1'b1;

else

cnt<=0;

end

always@(posedge clk or posedge rst)

begin

if(rst)

begin

temp<=0;

quotient_tmp<=0;

end

else if((start|start_dl)&&temp>=b_reg)

begin

temp<={temp-b_reg,a_reg[3]};

quotient_tmp<=(quotient_tmp<<1)+1'b1;

end

else if((start|start_dl))

begin

temp<={temp,a_reg[3]};

quotient_tmp<=quotient_tmp<<1;

end

else

begin

temp<=0;

quotient_tmp<=0;

end

end

always@(posedge clk or posedge rst)

begin

if(rst)

begin

quotient<=0;

remainder<=0;

result_valid<=0;

end

else if(start_dl2&&(!start_dl))

begin

quotient<=quotient_tmp;

remainder<=temp>>1;

result_valid<=1;

end

else

begin

quotient<=0;

remainder<=0;

result_valid<=0;

end

end

endmodule

tb如下:

module tb();

reg clk=1;

reg rst=1;

reg [3:0]a;

reg [3:0]b;

reg valid;

always #5 clk=~clk;

initial begin

#100 rst=0;

#100

a=4'b1011;

b=4'b0011;

valid=1'b1;

#10

valid=0;

end

division inst_division

(

.clk (clk),

.rst (rst),

.a (a),

.b (b),

.valid (valid),

.quotient (quotient),

.remainder (remainder),

.result_valid (result_valid)

);

endmodule

仿真结果如下:

热门推荐

王楚钦/孙颖莎巴黎奥运会混双夺冠之路:赛制考验与技战术精妙解析

门阀制度:中国古代社会的一种特殊结构

煤炭城市转型升级之七台河篇

咳咳咳,白天不咳晚上咳,注意鼻后滴漏综合征!

2024年十大语文差错公布,快来看这些常见误用!

温州十大街边小吃,接地气但十分美味!最后一个有上百年的历史了!

常吃葛根粉的七大好处

数字赋能诉讼服务 打造司法便民“三部曲”

干眼问题好不了?证实中医「针刺疗法」促进泪液分泌改善,论文登国际期刊

前端JS拼接字符串如何加空格

BGA封装焊接技术详解:从准备到后期处理的完整指南

德系、美系和法系车型在高速行驶稳定性方面的特点分析

身体在何时备孕怀孕几率较大?

如何把熊猫做成数字人视频

项目多公章怎么管理

“富不过三代”的真正含义

高速行驶中出现耳鸣的解决办法是什么?这种耳鸣现象的原因是什么?

一部手机能用多久?这5个信号告诉你该换了。

“绒馍馍”成新晋顶流:西安文创如何玩转创意与文化

蓟花:苏格兰之花的神秘与坚韧

淞沪会战全过程详解:血与火的正面交锋

企业上市辅导全攻略:流程与内容详解

红楼梦:明明是作者“哭成此书”,为什么要说是林黛玉还泪?

开放与改革:“先锋广州”的新方位

盗抢险理赔的步骤有哪些?这些步骤如何影响理赔效率?

桂圆一天吃几个合适?吃多了对身体有哪些不利影响?早做了解

糖尿病患者如何选择合适的食材?医生推荐这5类食物

灵活掌握牛肉炒制时间:根据个人口味调整熟度的建议

胆汁反流怎么检查出来

南京林业大学:完善志愿服务体系 服务育人工作创新发展