一篇文章说明常见的AI芯片高速互连方案

创作时间:

作者:

@小白创作中心

一篇文章说明常见的AI芯片高速互连方案

引用

1

来源

1.

https://www.scensmart.com/news/one-article-explains-common-high-speed-interconnect-solutions-for-ai-chips/

随着AI芯片技术的不断发展,高速互连方案成为了提升芯片性能的关键技术之一。本文将详细介绍NVIDIA的NV Link和NV Switch技术的发展历程及其性能参数,并对华为的NPU互连方案进行说明。

NVIDIA NV Link技术发展

产品 | 发布时间 | 显卡 | 连接数量 | GPU 之间总带宽 | 应用架构 |

|---|---|---|---|---|---|

NV Link 1.0 | 2016 | P100 | 4 | 160 GB/s | Pascal |

NV Link 2.0 | 2017 | V100 | 6 | 300 GB/s | Volta |

NV Link 3.0 | 2020 | A100 | 12 | 600 GB/s | Ampere |

NV Link 4.0 | 2022 | H100 | 18 | 900 GB/s | Hopper |

NV Link 5.0 | 预计 2025 | B200 | 18 | 1800 GB/s | Blackwell |

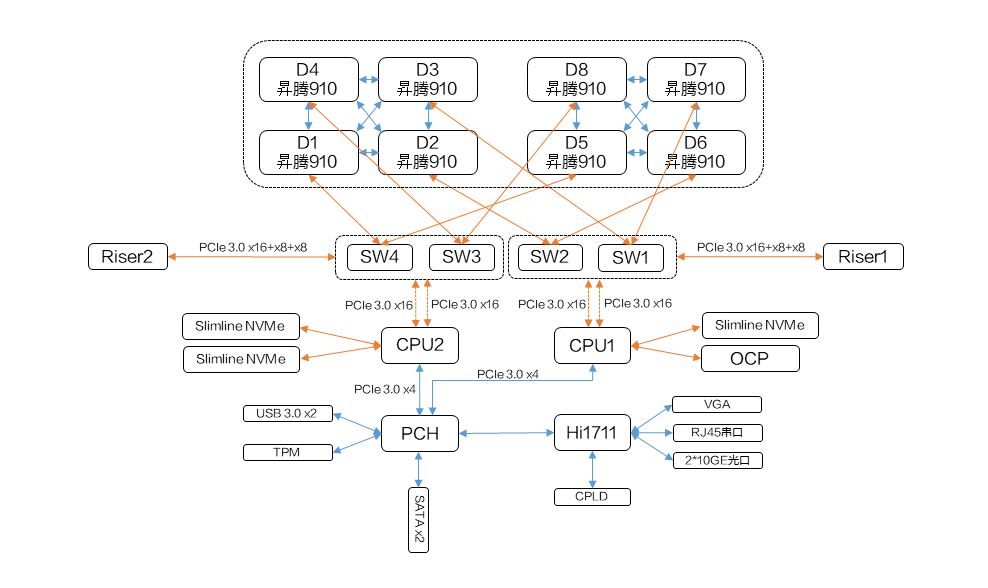

华为NPU互连方案

npu-smi info -t topo

NPU0 NPU1 NPU2 NPU3 NPU4 NPU5 NPU6 NPU7 NPU8 NPU9 NPU10 NPU11 NPU12 NPU13 NPU14 NPU15 CPU Affinity

NPU0 X HCCS HCCS HCCS HCCS HCCS HCCS HCCS PIX PHB PHB PHB SYS SYS SYS SYS 0-43,88-131

NPU1 HCCS X HCCS HCCS HCCS HCCS HCCS HCCS PHB PIX PHB PHB SYS SYS SYS SYS 0-43,88-131

NPU2 HCCS HCCS X HCCS HCCS HCCS HCCS HCCS PHB PHB PIX PHB SYS SYS SYS SYS 0-43,88-131

NPU3 HCCS HCCS HCCS X HCCS HCCS HCCS HCCS PHB PHB PHB PIX SYS SYS SYS SYS 0-43,88-131

NPU4 HCCS HCCS HCCS HCCS X HCCS HCCS HCCS SYS SYS SYS SYS PIX PHB PHB PHB 44-87,132-175

NPU5 HCCS HCCS HCCS HCCS HCCS X HCCS HCCS SYS SYS SYS SYS PHB PIX PHB PHB 44-87,132-175

NPU6 HCCS HCCS HCCS HCCS HCCS HCCS X HCCS SYS SYS SYS SYS PHB PHB PIX PHB 44-87,132-175

NPU7 HCCS HCCS HCCS HCCS HCCS HCCS HCCS X SYS SYS SYS SYS PHB PHB PHB PIX 44-87,132-175

NPU8 PIX PHB PHB PHB SYS SYS SYS SYS X HCCS HCCS HCCS HCCS HCCS HCCS HCCS 0-43,88-131

NPU9 PHB PIX PHB PHB SYS SYS SYS SYS HCCS X HCCS HCCS HCCS HCCS HCCS HCCS 0-43,88-131

NPU10 PHB PHB PIX PHB SYS SYS SYS SYS HCCS HCCS X HCCS HCCS HCCS HCCS HCCS 0-43,88-131

NPU11 PHB PHB PHB PIX SYS SYS SYS SYS HCCS HCCS HCCS X HCCS HCCS HCCS HCCS 0-43,88-131

NPU12 SYS SYS SYS SYS PIX PHB PHB PHB HCCS HCCS HCCS HCCS X HCCS HCCS HCCS 44-87,132-175

NPU13 SYS SYS SYS SYS PHB PIX PHB PHB HCCS HCCS HCCS HCCS HCCS X HCCS HCCS 44-87,132-175

NPU14 SYS SYS SYS SYS PHB PHB PIX PHB HCCS HCCS HCCS HCCS HCCS HCCS X HCCS 44-87,132-175

NPU15 SYS SYS SYS SYS PHB PHB PHB PIX HCCS HCCS HCCS HCCS HCCS HCCS HCCS X 44-87,132-175

Legend:

X=Self

SYS=Path traversing PCIe and NUMA nodes. Nodes are connected through SMP, such as QPI, UPI.

PHB=Path traversing PCIe and the PCIe host bridge of a CPU.

PIX=Path traversing a single PCIe switch

PXB=Path traversing multipul PCIe switches

HCCS=Connection traversing HCCS.

NA=Unknown relationship.

NVIDIA NV Switch技术发展

产品 | 直连或节点中 GPU 数上限 | GPU 间带宽 | 应用架构 |

|---|---|---|---|

NV Switch 1.0 | 8 | 300 GB/s | Volta |

NV Switch 2.0 | 8 | 600 GB/s | Ampere |

NV Switch 3.0 | 8 | 900 GB/s | Hopper |

热门推荐

肩周炎怎么按摩比较好的方法

辅助生殖进医保,各地政策有何不同?

【理论探索】深化零基预算改革:实践探索与改革思路

软件测试中的等价类划分方法详解

性激素六项和AMH检查时间一样吗?可以一起查吗?

项羽为何跟刘邦说曹无伤是告密者?原因令古人钦佩,现代人汗颜!

雇主责任险如何赔偿?赔偿标准如何确定?

从“康定斯基的宇宙”,再看20世纪的几何抽象

中药炙远志的功效与作用

产品检验报告真实性的重要性及确保方法

命理学:预测师命学基础理论汇总

探索服务器硬件:理解基础组件及其重要性

电动汽车电池热管理:液冷技术的现状与未来

120国家急救日——关爱生命,“救”在身边

重大突破!世界最大跨度斜拉桥钢桁梁吊装全部完成

智能窗户控制系统的设计与实现

韦小宝的7个老婆中,谁才是真心爱小宝?不是双儿也不是沐剑屏。

提升手机网速的实用技巧与解决方案总结

疟疾的中医辨证及治疗

1996年属鼠女生的性格特点与命运分析

高效液相色谱仪在药物分析中的应用

氨咖黄敏胶囊治疗感冒有用吗

js 实现手机摇一摇功能的完整指南

虚拟机如何摇一摇?三种实现方法详解

冬至过后哪些水果不宜吃?冬季饮食调理指南

算法工程师必修的相关专业有哪些

如何通过投资实现财富的保值增值?这些投资方式有哪些选择标准?

3月开始运势上行,财富大利,东山再起的四大生肖

购房后,房产证如何办理?

广东率先开启“AI农业”全面探索:科技赋能农业兴,以赛促研创新魂