Verilog基础:非门、与门、或门、或非门和异或非门的原理及代码实践

创作时间:

作者:

@小白创作中心

Verilog基础:非门、与门、或门、或非门和异或非门的原理及代码实践

引用

CSDN

1.

https://blog.csdn.net/qq_39646880/article/details/137023115

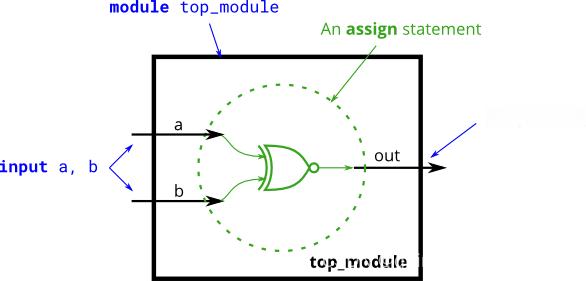

Verilog是一种硬件描述语言,广泛应用于数字电路设计。本文将介绍Verilog中几种基本逻辑门的原理及其代码实现,包括非门、与门、或门、或非门和异或非门。

非门(NOT Gate)

非门是最简单的逻辑门,它有一个输入和一个输出。非门的输出是其输入的逻辑非。如果输入为高电平(逻辑1),则输出为低电平(逻辑0);如果输入为低电平(逻辑0),则输出为高电平(逻辑1)。

Verilog代码实现

module not_gate (

input wire in, // 输入信号

output wire out // 输出信号

);

// 使用assign语句创建一个非门

assign out = ~in;

endmodule

与门(AND Gate)

与门有两个或更多的输入和一个输出。与门的输出是其所有输入的逻辑与。只有当所有输入都是高电平时,输出才是高电平;否则,输出为低电平。

Verilog代码实现

module and_gate (

input wire a, // 第一个输入信号

input wire b, // 第二个输入信号

output wire out // 输出信号

);

// 使用assign语句创建一个与门

assign out = a & b;

endmodule

或门(OR Gate)

或门有两个或更多的输入和一个输出。或门的输出是其所有输入的逻辑或。只要有一个输入是高电平,输出就是高电平;只有当所有输入都是低电平时,输出才是低电平。

Verilog代码实现

module or_gate (

input wire a, // 第一个输入信号

input wire b, // 第二个输入信号

output wire out // 输出信号

);

// 使用assign语句创建一个或门

assign out = a | b;

endmodule

或非门(NOR Gate)

或非门(NOR Gate)是逻辑或门(OR Gate)的输出经过非门(NOT Gate)的结果。在Verilog中,您可以使用assign语句来定义或非逻辑。下面是一个简单的例子,展示了如何创建一个两输入的或非门:

Verilog代码实现

module nor_gate (

input wire a, // 第一个输入信号

input wire b, // 第二个输入信号

output wire out // 输出信号

);

// 使用assign语句创建一个或非门

// 或非逻辑是输入的逻辑或的结果取反

assign out = ~(a | b);

endmodule

异或非门(XNOR Gate)

异或非门是异或门(XOR Gate)的输出经过非门的结果。异或门有两个输入,其输出是输入的逻辑异或。如果输入信号相同(都是高电平或都是低电平),则输出为高电平;如果输入信号不同,则输出为低电平。异或非门则将这个输出再取反。

Verilog代码实现

module xnor_gate (

input wire a, // 第一个输入信号

input wire b, // 第二个输入信号

output wire out // 输出信号

);

// 使用assign语句创建一个异或非门

// 异或非逻辑是输入的异或结果取反

assign out = ~(a ^ b);

endmodule

在编写Verilog代码时,您可以将这些基本逻辑门组合起来,形成更复杂的数字电路。每个模块都可以作为一个独立的单元,通过输入输出端口与其他模块连接。通过这种方式,您可以构建从简单的逻辑电路到复杂的数字系统的一切。

热门推荐

《火影忍者》中的忍者与神怪文化探秘

《火影忍者》手游:快速提升战力秘籍

大蛇丸的蛇之忍术:揭秘《火影忍者》最致命的魅力!

《火影忍者》手游:高效攻略助你轻松200活跃度!

打卡潘涂海蛎夜市,感受厦门美食魅力!

秋冬吃货天堂:八市必打卡厦门美食

厦门小吃:闽南文化的味蕾记忆

上郭头村农村不动产登记:创新实践与成效

夜空中最亮的星是哪颗星?

珠峰探险:喜马拉雅的极致美景

五代十国:南北经济大不同

蜘蛛网能黏万物,为啥黏不住蜘蛛?

春节三亚旅游:全面攻略及费用、住宿、穿衣指南

昆明启程:探秘云南风情,必玩景点攻略指南

家庭网络优化指南:提升NAT类型,降低游戏延迟、提高下载速度

蜘蛛的捕食方式和网结构

海蜘蛛用5亿年亲身证明了一个道理:“只要足够没用,就没天敌”

蜘蛛的生态位与适应性

《危险的她第二季》:女性力量的觉醒与互助

冬日苏州必打卡:拙政园、留园、虎丘二日游攻略

探秘苏州古典园林:真珠舍利宝幢与退思园的秘密

秋冬打卡苏州三大名园:拙政园、留园、网师园

在兰州,如何快速适应高原生活?

兰州:高海拔塑造的独特气候体验

备战“兰马”,如何应对高海拔挑战?

看僵尸片能为新冠打心理预防针?

从“喜剧小天才”到消防员:《僵尸先生》小僵尸何健威的别样人生

从《僵尸叔叔》到《一眉道人》:那些年我们追过的“小僵尸”

赵本山:从农村走出的“小品王”

五代十国南方经济特色分析:专家推荐必读